Neuromorphic Hardware Guide

Explore cutting-edge neuromorphic chips and architectures, featuring innovative designs and advanced neural processing technologies.

Welcome to the Open Neuromorphic Hardware Guide. This directory provides a comprehensive overview of neuromorphic hardware, from pioneering past projects to the latest commercial and research chips. Each entry includes key specifications, architectural details, and links to relevant publications. For definitions of common terms, please see the glossary below.

2026

2025

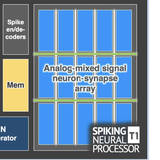

TSP1 - Applied Brain Research

AnnouncedThe TSP1 is a time-series, brain-inspired chip designed for ultra-low power edge AI applications, delivering automatic speech recognition recognition at <35mW, supporting state-space network processing for real-time time-series inference.

Pulsar - Innatera

Mixed-signal ReleasedPulsar is a brain-inspired neuromorphic microcontroller designed for ultra-low-power, real-time intelligence in edge devices. It combines a Spiking Neural Network (SNN) engine with a RISC-V MCU and CNN acceleration to enable smart sensing applications without cloud dependency.

2024

2023

DYNAP-SE2 - Institute of Neuroinformatics

Mixed-signal ReleasedThe DYNAP-SE2 is a configurable, mixed-signal neuromorphic chip featuring 1024 neurons, 65k plastic synapses, specialized dendrites, low-latency event routing, and multi-timescale adaptation dynamics. This enables real-time prototyping of biologically inspired spiking neural networks for ultra-low power edge processing.

NorthPole - IBM

Digital ReleasedNorthPole is a neural inference architecture that blurs the boundary between compute and memory by eliminating off-chip memory and intertwining compute with memory on-chip. It is a low-precision, massively parallel, and energy-efficient spatial computing architecture.

2022

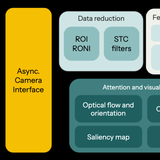

Speck - SynSense

Digital, with analog sensor ReleasedSpeck is a fully event-driven neuromorphic vision SoC. Speck is able to support large-scale spiking convolutional neural network (sCNN) with a fully asynchronous chip architecture. Speck is fully configurable with the spiking neuron capacity of 328K. Furthermore, it integrates the state-of-art dynamic vision sensor (DVS) that enables fully event-driven based, real-time, highly integrated solution for varies dynamic visual scene. For classical applications, Speck can provide intelligence upon the scene at only mWs with a latency of 3.36us for a single event processed by a 9 layer network.

Akida - BrainChip

Digital Released On-Chip LearningBrainChip's Akida is an ultra-low-power neuromorphic processor inspired by the brain's neural architecture. It accelerates complex AI at the edge through event-based processing, on-chip learning abilities, and support for advanced neural networks like CNNs, RNNs & custom Temporal Event-based Nets.

SENeCA by imec

Digital Released On-Chip LearningSENeCA is a RISC-V-based digital neuromorphic processor targeting extreme edge applications by accelerating Spiking Neural Networks inside or near sensors and small devices where ultra-low power and adaptivity are required. It inherits fundamental properties from the biological brain: spatio-temporal sparsity exploitation, parallel processing, infinite scalability, low-precision parameters, asynchronous non-deterministic execution, adaptation and fault-tolerance architecture, interconnect of neuron cluster cores with RISC-V-based instruction set.

BrainScaleS-2 — Heidelberg University

Mixed-signal Released On-Chip LearningThe BrainScaleS-2 is an accelerated spiking neuromorphic system-on-chip integrating 512 adaptive integrate-and-fire neurons, 131k plastic synapses, embedded processors, and event routing. It enables fast emulation of complex neural dynamics and exploration of synaptic plasticity rules. The architecture supports training of deep spiking and non-spiking neural networks using hybrid techniques like surrogate gradients.

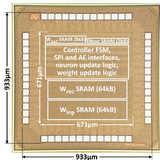

ReckOn - Charlotte Frenkel

Digital Released On-Chip LearningReckOn demonstrates, for the first time, end-to-end on-chip learning over second-long timescales (no external memory accesses, no pre-training). It is based on a bio-inspired alternative to backpropagation through time (BPTT), the e-prop training algorithm, which has been modified to reduce the memory overhead required for training to only 0.8% of the equivalent inference-only design. This allows for a low-cost solution with a 0.45-mm² core area and a <50-µW power budget at 0.5V for real-time learning in 28-nm FDSOI CMOS, which is suitable for an always-on deployment at the extreme edge. Furthermore, similarly to the brain, ReckOn exploits the sensor-agnostic property of spike-based information. Combined with code-agnostic e-prop-based training, this leads to a task-agnostic learning chip that is demonstrated on vision, audition and navigation tasks.

Xylo - SynSense

Digital ReleasedXylo is a 28nm 1000 neuron digital spiking neural network inference chip optimized for ultra-low power edge deployment of trained SNNs, with a flexible architecture to map various network topologies.

2021

Loihi 2 - Intel

Digital Released On-Chip LearningLoihi 2 is Intel's latest neuromorphic research chip, implementing spiking neural networks with programmable dynamics, modular connectivity, and optimizations for scale, speed, and efficiency. Early research demonstrates promise for low-latency intelligent signal processing.

SpiNNaker 2 - University of Dresden

Digital Released On-Chip LearningThe SpiNNaker2 chip houses 153 ARM cores with 19MB on-chip SRAM, 2GB DRAM, and dedicated Machine Learning (e.g., MAC) and Neuromorphic (e.g., Exp/Log) accelerators. Manufactured in 22nm FDSOI, it employs Adaptive Body Biasing (ABB) in a Forward Body Bias (FBB) configuration, as well as DVFS for adaptive near-threshold operation down to 0.5V, enabling a 10x increase in neural simulation capacity per watt over SpiNNaker1.

2020

2019

DynapCNN - SynSense

Digital ReleasedThe DynapCNN is an ultra-low power, event-driven neuromorphic processor chip for spiking neural networks that achieves sub-milliwatt computation using in-memory techniques. With 1M neurons, it can implement convolutional network models like LeNet and ResNet, interfacing directly to sensors like DVS cameras for low-latency, always-on vision applications.

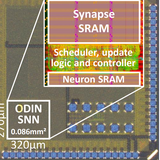

Odin by Charlotte Frenkel

Digital Released On-Chip LearningThe ODIN 256-neuron 64k-synapse neuromorphic processor highlights how design constraints on the synapses can be released by offloading most synaptic computations at the neuron level. All synapses embed spike-driven synaptic plasticity (SDSP), while neurons are able to phenomenologically reproduce the 20 Izhikevich behaviors of cortical spiking neurons. At the time of publication, ODIN demonstrated the highest synaptic density, and the lowest energy per synaptic operation among digital designs. ODIN was fabricated in 28nm CMOS and can be prototyped in small FPGAs.

2018

2016

2015

2014

TrueNorth - IBM

Digital RetiredTrueNorth is a 5.4B transistor, 4096 core, 1M neuron, 256M synapse neurosynaptic chip implemented in 28nm. Through a mixed async-sync design & custom toolflow, it achieves 58GSOPS & 400GSOPS/W efficiency while running neural networks in 65mW real-time.

NeuroGrid (BrainDrop) - Stanford

Mixed-signal RetiredNeurogrid is a specialized neuromorphic hardware system that enables real-time simulation of neural models with up to 1M neurons & 8B synapses using low-power mixed-signal silicon neuron circuits arranged in 16 chips & interconnected via multicast routing.

2006

Help Us Improve this Guide

Our hardware guide is community-maintained. If you know of a chip we should add, see an error, or have updated information, please let us know by opening an issue on our GitHub repository.

Glossary of Terms

Click to expand/collapse glossary +

Spiking Neural Network (SNN): A type of artificial neural network that closely models the spiking behavior of biological neurons, utilizing discrete spikes or pulses of activity for information processing.

Event-Driven Computation: A computing paradigm where processing occurs in response to specific events or stimuli, allowing for energy-efficient operation and asynchronous communication between components.

Synapse: The functional connection between two neurons or between a neuron and another cell, where signals are transmitted through chemical or electrical means.

Plasticity: The ability of synapses to strengthen or weaken over time, a key feature in neuromorphic hardware that enables learning and adaptation.

Spike-Timing-Dependent Plasticity (STDP): A type of synaptic plasticity in which the timing of neural spikes influences the strength of the synapse, essential for learning and memory in neuromorphic systems.

Memristor: A resistor with memory, a key component in neuromorphic hardware that can store and process information, mimicking the synaptic plasticity found in biological systems.

Neuromorphic Chip: A specialized hardware component designed to implement neuromorphic computing principles, often featuring a large number of simple, interconnected processing units.

Neuromorphic Engineering: The interdisciplinary field that combines principles from neuroscience, physics, computer science, and engineering to design and build brain-inspired computing systems.

Event-Based Sensor: A sensor that captures and transmits information in an event-driven manner, aligning with the principles of neuromorphic hardware for efficient and low-latency data processing.

SpiNNaker (Spiking Neural Network Architecture): A neuromorphic computing platform designed for simulating large-scale spiking neural networks, with a focus on real-time processing and parallel communication.